BING-JHEN HONG/iStock Editorial via Getty Images

Investment Thesis

I have been detailing the TSMC (NYSE:TSM) swan song over the last year (with the initial signs going back even further), as TSMC’s progress with regards to following Moore’s Law seems to have hit a similar wall as Intel (NASDAQ:INTC) back at 10nm.

In my view, with the latest information that has been revealed, which indicates that TSMC will go through a similar half a decade “dark age” without scaling as Intel at 10nm, there are now so many red flags that TSMC’s process leadership has now become completely untenable.

This was completely unthinkable not too long ago, proving how rapid TSMC’s technology position is deteriorating. Investors should be aware that TSMC soon will not be the industry leader anymore that they likely still think they are investing in. At that point, only inertia – and competitors’ ability to build new fabs quickly – will keep TSMC going. Still, I predict customers will rather quickly become dissatisfied with TSMC’s lack of progress, making Intel the undisputed beneficiary.

Background

Moore’s Law, which states that the number of transistors on a chip should double every two years, has been the golden candle to measure progress in semiconductors for more than half a century. Since the chip size stays roughly constant, this really means that transistor density (i.e. the number of transistors normalized for the same area) should double every two years.

The metric that has been popularized in that regard is MTr/mm2 (millions of transistors per square millimeter), which for convenience will be further abbreviated to simply MT. For example, Intel’s 10nm (renamed to Intel 7) has a density of 100MTr/mm2, or simply 100MT.

N5 worse than expected

Although N5, as the successor of N7 that TSMC took process leadership with from Intel in 2018, continued TSMC’S leadership when it was introduced in 2020 in the Apple (AAPL) A14, TSMC to date has remained very vague about the actual process specifications, besides saying that N5 was a 1.8x shrink compared to N7 (slightly worse than the 2x benchmark, but in-line with TSMC’s average shrink per node). This led many to conclude that N5 had a logic density of 171MT or even higher, far surpassing the 100MT of Intel’s most advanced 10nm/7 process.

However, new analysis from Angstronomics based on actual measurements shows that this has not been the case at all. While the first hints that N5 didn’t achieve its intended shrink already surfaced in 2020 when Apple reported the transistor count for the A14, the actual transistor measurements provide conclusive confirmation that N5 in fact only achieved a 1.52x shrink. This results in a density of “just” 138MT.

As the tweet above suggests, TSMC seems to have been flat out lying, or made misleading statements at best. To investors, this should come across as a red flag.

N3 also worse than expected

As investors know, the key to building wealth is compounding returns. However, the reverse is also true: compounding at a lower CAGR will significantly decrease the cumulative long-term returns.

So given the lower-than-expected shrink that N5 brought, this flows through to N3, which is hence also delivering a lower-than-expected density. As case in point, a few years ago it had been expected that N3 would deliver a density of around 300MT. However, the above information yields a new (preliminary) density estimate of just 215MT.

While a lower density certainly decreases the absolute competitiveness of the node, what ultimately matters is the relative competitiveness, as for example Intel has since also delayed its 7nm node (renamed to Intel 4).

In that regard, recently quite a bit of information was revealed by Intel at a conference. What was most surprising is that Intel 4 has been relegated to basically just a stopgap node with only one, high performance, logic library. For comparison, previous nodes had three libraries plus further features such as I/O and analog.

So while Intel 4 delivers a 2x scaling (since CPUs heavily use high performance libraries), the theoretical maximum density of the node (which is the subject of this article) is just 123MT. Hence, it won’t be until Intel 3 in early 2024 that Intel will again deliver a major jump in density. According to my analysis a 2-1 library (the numbers represent the number of fins per PMOS and NMOS transistor) should deliver a density of about 200MT, while a 1-1 library could deliver a density of over 230MT, surpassing TSMC’s N3. Although TMSC is working on a N3S node with higher density, its precise timing is not known yet.

For completeness, note that for now this is speculation as Intel hasn’t even officially confirmed that Intel 3 will have a HD library, only that it will have a “higher density HP library”. Nevertheless, every one of Intel’s FinFET nodes (since 22nm) has had a HD library, which would make it surprising if Intel 3 didn’t have one, especially since Intel 3 is also targeted for Intel Foundry Services customers. In addition, my speculation about a 2-1 or 1-1 fin library was made before TSMC announced its own N3 2-1 library, and N3S is likely a 1-1 library; this validates that a 2-1 library is plausible. In summary, a 2-1 library would put Intel basically on par with TSMC, both in terms of fin count but also overall transistor density (roughly 200MT for Intel 3 vs. 215MT for N3). Although Intel would be a year later in terms of time to market.

Overall, this is a mixed bag. My initial analysis in 2020 had indicated that Intel 4 (back then called 7nm) would land somewhere between N5 and N3 with regards to transistor density. However, based on current information, Intel 4 actually seems closer to N3 than N5 when only considering the HP (high performance) library, while Intel 4 significantly trails in maximum density given the lack of a HD (high density) library. As such, it won’t be until Intel 3, one year after Intel 4 (and N3), that Intel will introduce a new HD library. Similar to the case of the HP library, though, the Intel 3 HD library should actually be nearly on par to N3.

Third time’s a charm? Nope, N2 also worse than expected

Not only is Intel 3 significantly closer to TSMC N3 than previously expected, but N2 has likewise been defying expectations to the downside. As previously detailed, the timing of N2 has put the node on a 3-year cadence from N3, which itself was already on a relatively slow 2.5-year cadence while also bringing just a mediocre ~1.55x shrink.

But the bloodbath continues even further. TSMC recently provided some more information about N2 at its Technology Symposium, and it was quite awful. TSMC said it expects N2 to bring a “>1.1x” shrink. This number is based on a chip composition of 50% logic, 30% SRAM and 20% analog. Even when assuming that SRAM and analog do not shrink at all, then logic scaling should be around 20-30% (unless TSMC is for some reason significantly lowballing the >1.1x number).

Ultimately, this means that in 2026 when N2 launches in the market, TSMC will deliver a transistor density that people until recently had actually been expecting from N3 in 2023.

Scaling trends vs. Intel

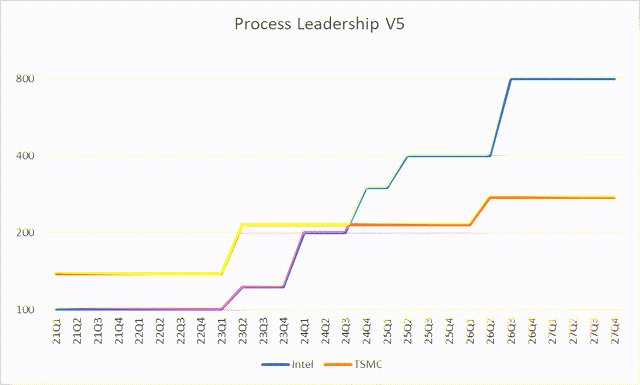

If the above sounds like TSMC will not be competitive and lose its leadership position, this seems correct. While as noted above there is no official confirmation yet, Bob Swan in late 2019 had stated that both 7nm (Intel 4/3) and 5nm (20A/18A) would deliver a 2x shrink. Since then, Intel has further said it could achieve a further 40-100% increase in density at the node beyond 20A/18A. Taken at face value, this means that by early 2025 Intel might deliver a transistor density of 400MT and up to 800MT by 2026. From the discussion above, the nearly complete lack of scaling of N2 means that TSMC might hardly even reach 300MT in 2026.

This means that in the worse case, Intel could have 3x the transistor density of TSMC by 2026. This would be a staggering and very quick demise.

Overall, from N5 to N3 to N2 (which in time is from Q3’20 to Q2’26), TSMC will deliver about a 2x scaling in six years, representing a CAGR of 13%. In contrast, from Intel 4 to 3 to 20A to 18A to 14A (which in time is from Q2’23 to Q4’26), Intel will deliver about a 6.5x scaling in 3.5 years.

Own work

To be clear, for TSMC the numbers until N3 are basically confirmed, while N2 as discussed represents only a minor shrink, according to TSMC itself (“>1.1x”). For Intel the numbers until Intel 4 are confirmed, while Intel 3 assumes a 2x shrink from Intel 7 and Intel 18A assumes a 2x shrink from Intel 3. This information comes from Bob Swan in 2019 talking at the time about “7nm” and “5nm” shrinks. Obviously, there is the possibility that some of these targets have been changed in the last three years.

Lastly, the 14A node in 2026 assumes another 2x shrink. This node also has some assumptions, although the overall assumption is that Intel will simply target to continue to follow Moore’s Law. For example, in October 2021 Pat Gelsinger said that combined with Intel’s 3D packaging, he expects Intel to go faster than Moore’s Law for the next decade. In particular, it is assumed that this node introduces the “CFET” transistor architecture that Intel disclosed in December 2021 with the comment that this could deliver a 30-50% shrink. While the 50% shrink (2x density) assumed here is at the high-end of that range, Intel would still retain its leadership even if 14A delivered a 0% shrink.

Conclusion

Intel has set itself the goal to continue Moore’s Law with a 2x scaling in transistor density every node (every two years). In order to regain process leadership, Intel is making up for the Intel 4 delay by accelerating the cadence to 20A (just about 18 months between these two nodes).

TSMC, on the other hand, started to significantly slow its density scaling at N5 (~1.5x) and coming to a near-standstill at N2 (est. ~1.25x), while also significantly slowing its cadence to 2.5 at N3 and 3 years to reach N2.

Risks and caveats

The major caveats have already been mentioned, but it may be prudent to repeat them.

The main difficulty, as Intel’s disclosure of its Intel 4 has illustrated, is that process technologies and actual chips usually consist of a few different “cell libraries” that each have different trade-offs with regards to performance, power and area (PPA).

First, this means that the discussion in this article is a bit academic. For example, Intel (for the most part) doesn’t even use the 100MT HD library for its CPUs in the first place, since CPUs are designed to reach the highest possible clock speed (performance). Nevertheless, as the Angstronomics article citied above illustrated, there is still a strong correlation between the theoretical and practically realized transistor density. As a hypothetical example, if both Intel 3 and TSMC N3 have a density of about 210MT, then an Apple SoC manufactured on both processes should result in roughly the same chip size.

Secondly and more importantly, different libraries may achieve different shrinks across nodes. In this case, while Intel has detailed how the Intel 4 HP library achieves a 2x shrink, it cannot be stated with certainty yet how this will translate into for example the HD library of Intel 3. In fact, the Intel 4 node doesn’t even have a HD library in the first place. This change in practice also introduces some question marks for 20A and 18A. Although, due the pull-in of 18A this node will be about half a year behind 20A compared to a full year for Intel 3 (vs. Intel 4).

As such, the extrapolation that Intel could reach a density of 400MT in 2024 and 800MT in 2026 is not certain and hence may have to be revised (if there is no HD library availability in that year). Nevertheless, since the information provided by TSMC implies that it will reach 215MT in 2023 and around 270MT in 2026, the margin of safety for Intel to regain transistor density leadership seems incredibly large, even if Intel’s density turns out to be less than currently expected.

The last risk is more psychological. Back around 14nm, Intel continually made a lot of noise about its transistor density leadership. In contrast, currently Intel management has still said absolutely nothing about regaining transistor density leadership. The only thing Intel has yet claimed is that it would regain performance per watt process leadership by 2025. One would assume that Intel management would scream from the rooftops (as it had done at 14/10nm initially) if it would really achieve a material advantage over TSMC (as this article indicated). The fact that as mentioned Intel hasn’t talked about transistor density at all could lead to some prudence.

As mentioned above, the validation to assume a 2x shrink for all of Intel’s forthcoming comes from former CEO Bob Swan’s comment in 2019, as well as Pat Gelsinger’s statement that it would follow Moore’s Law for the next decade. As previously discussed, one reason for TSMC falling behind may be trouble in developing gate-all-around transistors.

Investor Takeaway

I currently believe TSMC’s process leadership is falling apart more significantly than anyone (including myself) had previously expected.

First, actual measurements confirm that N5 is at least 20% (~1.25x) less dense than what had previously been reported in technical publications. Secondly, due to the laws of compounding this means that N3 is also less dense than what had previously been expected. This in turn means that Intel 3 might nearly match N3. Thirdly, whereas Intel will follow up on Intel 3 with 20A and 18A within respectively 6 and 12 months, TSMC has put N2 on a long 36 month cadence. In addition, TSMC’s latest disclosures indicate that logic transistor density will increase by less than 30%.

In that sense, Intel catching up will be similar to how TSMC gained its process leadership in the first place: simply by (nearly) following Moore’s Law while others are having issues that are slowing them down considerably.

This ultimately implies that TSMC will lose its density leadership incredibly fast and by an incredible amount. Intel will nearly catch up to N3 in early 2024 with Intel 3, achieve a nearly 2x leadership within the next year with 20A/18A, and then further increase its leadership to up to 3x by the end of 2026.

It seems very unlikely that such a change in the technology landscape would not eventually also impact TSMC’s financials. Either indirectly as Intel gains market share due to superior technology, or directly as TSMC customers move to Intel Foundry Services as their new #1 foundry.

Be the first to comment