BING-JHEN HONG/iStock Editorial via Getty Images

Investment Thesis

Taiwan Semiconductor Manufacturing Company (TSM) reported an absolutely stunning quarter. And given that there is no in end in sight for TSMC’s massive capex spending (resulting in much higher capacity), combined with its major price increases TSMC’s medium-term future looks very bright.

However, in order to measure the long-term potential of TSMC, one must look not at the financial but at the technological trends. Here, the picture has gone from bad to worse in the matter of a few quarters. Not only has the extent of the N3 delay become clear over this time period, but during the recent earnings call, TSMC presented a very bleak picture for its N2 process. In short, TSMC is likely finished.

The simplest way to illustrate how much TSMC surprised me is this: I have never been a TSMC bull, yet the timing that TSMC announced for N2 was 4-5 quarters later than (the already quite bleak timing) I had told investors about just two quarters ago.

If this was Intel (INTC) the stock would be collapsing right now. Hence, it is now also clear why Pat Gelsinger is so intent on Intel building fabs like tree leaves sprouting in the spring, in order to capitalize on its competitor’s stumble/complacency.

Background

I have been detailing the 3nm, and now also 2nm, train wreck for quite a while now:

TSMC confirms 2nm delay

One never really knows if analysts of tech companies will ask relevant questions, or just ask about the financials. Luckily for investors (and unluckily for TSMC), during the recent Q1 earnings call, it was clear that analysts had been paying close attention to the developments of TSMC’s competitors in the foundry space. So ask questions they did.

First, as a quick refresher, it was half a year ago that TSMC strongly suggested that its 2nm node would be delayed (following the delay of 3nm) by stating the 2nm would only go in production in 2025. For a quick check, take 5nm’s production start in Q2 2020 and add four years (the equivalent of two nodes). Hence, a production start in 2025 implies a cadence of 2.5 years for two consecutive nodes. This is markedly slower than Moore’s Law’s golden standard of two years per node.

However, admittedly TSMC did leave quite some room for interpretation in its statement half a year ago. After all, TSMC might have referred to 2025 for when products would be in the market. For example, if 2nm production started two years after 3nm (which would be a normal schedule), then production could start in the second half of 2024 with products in early 2025. Indeed, in my previous analysis I put TSMC’s 2nm launch in Q1 2025.

Alas, this appears not to be the case. Let’s just consider what TMSC said after the questioner pointed out that its competitors had “accelerated their schedule” for 2nm, while TSMC was remaining silent.

CEO C. C. Wei: Our N2 development is on track, including new transistor structure and progressing to our expectation. We expect our N2 delivery to be the best technology, maturity, performance and cost for our customers. And we are confident that N2 will continue our technology leadership to support our customer growth. And we still plan the production in 2025.

Oof. Remember that not too long, investors and tech enthusiasts expected 3nm to go into production by mid-2022 – in a few months. There had been many, many people who thought that Apple (AAPL) would launch a 3nm iPhone this year. (I was arguably the first, back in early 2020, to suggest this could not be the case.) Instead, several months ago it became apparent that 3nm had slipped to the last quarter, and perhaps even the last month, of 2022.

Hence, this means that TSMC’s statement that 2nm is scheduled for 2025 conclusively confirms that 2nm is also delayed: TSMC by definition won’t be able to meet a two year schedule. Although TSMC denied it wasn’t denied, one should take these management comments with a grain of salt, as marketing fluff, since Moore’s Law is (the only) yardstick by which one can measure companies’ progress in the semiconductor industry. More on this below.

But it gets even worse. Apparently, analysts still weren’t fully satisfied by TSMC’s comments. A while later in the call, one analyst remarked that TSMC, indeed, didn’t maintain a two year cadence with 3nm, and wondered if TSMC planned to go back to two years with 2nm. Let’s hear what TSMC had to say:

CEO C. C. Wei: Brett, our progress so far today for the N2 is on track. And all I want to say is, yes, at the end of 2024, you will enter the risk production. 2025, it will be in production, probably close to the second half or the — or the end of 2025. That’s our schedule.

With this information, one can conclude following verdict. After a 2.75 year cadence at 3nm to deliver a measly 1.6x density improvement, TSMC has now scheduled 2nm at 3 year cadence (which could become even longer if there are any further delays) to deliver an as of yet unknown transistor density improvement.

To be clear and unambiguous, how investors should view this is that the 3 year cadence for N2 stacks on top of the 2.75 year cadence for N3. Those cadences imply respectively a 0.75 and 1 year delay compared to Moore’s Law. (It is actually even worse since Moore’s Law implies a 2x shrink, while as stated above 3nm will deliver just a 1.6x improvement.) In other words, when taking 5nm as a baseline, TSMC is “on track” to deliver 2nm with what in reality amounts to a 1.75 year delay.

To let the gravity of this announcement sink in, what this all amounts to is that TSMC just announced a 1 year delay of its 2nm process. For comparison, Intel stock dropped a whopping 20% the day it announced that 7nm would be delayed by 6-12 months.

So if this were Intel, the stock would have collapsed, but instead the stock didn’t even blink. To extent the analogy, what TMSC has basically done is as if Intel had never told investors (in 2019) that it aimed to launch 7nm in 2021, went silent for a couple years, and then announced that 7nm (now renamed to Intel 4) was “on track” to go into production in the second half of 2022. But wait a second, didn’t 10nm go into production in the second half of 2019 already, which implies a 3 year cadence and hence a 1 year delay?

Exactly. If Intel had never announced anything about 7nm (Intel 4), then it wouldn’t have had to tell investors anything about how under the hood Intel had discovered a “defect mode” that had resulted in a 1 year delay, and how Intel then significantly redesigned this node to use much more EUV layers, so the node is now on track (to the revised schedule). Instead, Intel had decided (in 2019) to be open about its roadmap, which then backfired. Investors could then basically follow “live” (quarterly) how Intel tried to recover from the delay, resulting in the CEO switch, etc.

Like I said, this is exactly how it is (not) going at TSMC, as TSMC has opted to remain silent. So instead, investors needed to rely on rumors (which then got covered in articles like this one) to find out that TSMC had a somewhat similar issue as Intel: whereas Intel used too few EUV layers at Intel 4 and needed to redesign the node, TSMC had to redesign N3 with less EUV layers, and hence also a lower density shrink.

With regards to N2, it is anyone’s guess what issue or issues TSMC is having. However, we can make one educated guess: the FinFET is running out of steam, which requires a completely new transistor to be introduced, the gate-all-around. Without patting myself too much on the back, anyone who has read some of my analysis shouldn’t be too surprised that Intel is able to use this transition to regain process leadership while Intel is running behind, as I highlighted Intel’s world-class components research already two years ago: Intel Vs. TSMC: Process Technology Leadership Is More Than Transistor Density (NASDAQ:INTC). Many people thought Intel had become a dinosaur destined for irrelevance, but those people years down the road are now finally getting disproved.

Lastly, analysts also poked about the change in ASML (ASML) lithography leadership, and the answer is very similar to the last ones: management preferred to refer to its present leadership position rather than actually answer questions about the future.

CEO C. C. Wei: Well, let me answer the question. We are the largest user of EUV tool today in the industry. And so we have intensively evaluated and are very familiar with those high-end EUV tools for wire. And we will continue to evaluate and adopt the high-end tool whenever we think is necessary and is ready and cost effective. Whether it is a N2 or not, I have not yet to be able to share with you.

In stark contrast, while Intel has been shouting from the rooftops that it would be the first adopter of high-NA EUV in 2025 (including support quotes from ASLM’s CEO), TSMC again choses to remain silent.

I have seen people suggest that TSMC would be just one quarter or so later than Intel (“Intel bought the first tool, but the second one will go to TSMC”), but this lack of confirmation may suggest that high-NA may follow much later for TSMC. At this point, the best-case may be something similar as to how TSMC originally introduced EUV, by introducing a derivative of N7 (N7 Plus) that used EUV (at a few layers) and was introduced a year or so after the initial N7.

I feel like I can’t emphasize this enough, but to me this is all very reminiscent to how I have seen Intel fall behind: as late as 2017, Intel management was putting out graphs (“Have you lost your lead? No!”) talking about how it was 3 years ahead of the competition at 14nm (TSMC’s equivalent node was 10nm), despite that just one year later, in 2018, Intel would fall behind for the next 6 years as competitors moved to 7nm (and then 5nm and 3nm) while Intel struggled with 10nm (and then 7nm aka Intel 4).

Process leadership

To summarize, literally in the last two months, we now seen two updates from two competitors, each in the opposite direction: Intel has pulled in 18A by 6 months while TSMC has delayed N2 by 12 months.

With this information, it is possible to make a new graph to show how process leadership will evolve over the coming years. If people until now were still giving TSMC any benefit of the doubt, then this latest information should just have all but erased this.

(Anecdotally, on Twitter I have seen many comments by people who are still giving TMSC exactly this benefit, but as mentioned above Intel was also full of confidence about how it was ahead at 14nm, but then simply was unable to deliver 10nm, which settled the debate. Note that before the 10nm delay and the smaller 14nm delay, Intel had an absolutely impeccable track record for at least 1.5 decades, similar to TSMC now.)

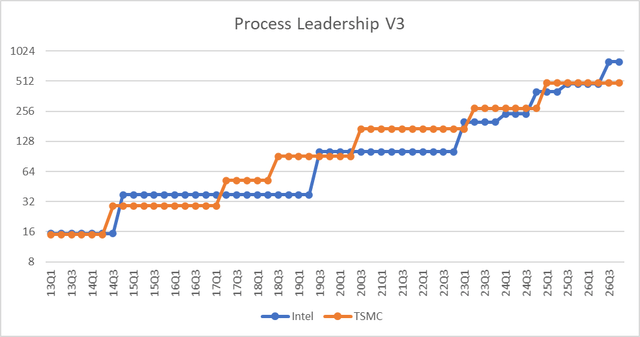

First, here is my previous graph (from late last year), which as discussed gave TSMC the benefit of the doubt by putting 2nm in Q1 2025:

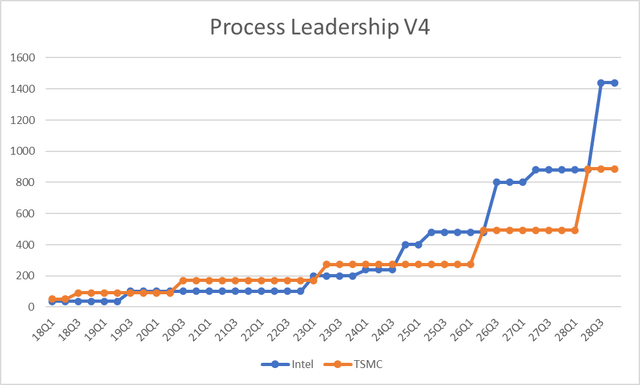

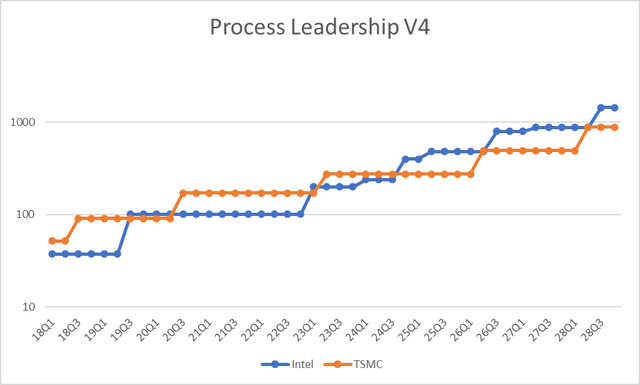

Now, here is the new graph:

Here is the same graph on a logarithmic scale:

Even though the graph should speak for itself (at the beginning the orange line is comfortable above the blue line, while at the end the blue line is comfortably above the orange line), some analysis is still in order to correctly interpret what is shown.

First, on the Intel side I have pulled in 18A by one quarter and left 14A unchanged. I view this as a conservative estimate given that officially 18A production has been pulled in by up to six months from Q1’25 to H2’24. The new schedule should allow products to hit the market by Q2’25.

How about 14A, which Intel hasn’t officially announced? There could be two schools of thought. First, the conservative investor might assume that Intel will be targeting a regular 2 year cadence compared to 20A, which implies production in the first half of 2026, and launch in the second half. This is what is displayed in the graph. However, given the pull-in of 18A, one could speculate that 14A might also be ahead of schedule. After all, Intel has said that it aims to deliver a yearly cadence of process nodes (tick-tock). In that case, 14A would launch one year after 18A and hence less than two years after 20A.

However, this would be akin to Intel Accelerated 2.0, since Intel would repeat the trick that it is doing at 20A (vs. Intel 4) by adhering to a cadence that is less than two years. Although as an Intel bull it is tempting to go with this scenario and deliver the final blow to TSMC’s leadership, for now let’s assume that Intel will not be this crazy. After all, CFO Dave Zisner promised investors that Intel would start to deliver strong gross margins and cash flows by 2025. (As I have explained previously, the accelerated cadence is one part of the reason why gross margin will remain low until 2024.)

For TSMC, I have had to delay 2nm by no less than 5 quarters. Since the quote above specifically stated “end of 2025” (Q4 2025), investors should not expect to see products in the market until Q2 2026.

With that said, some people may observe that I couldn’t resist to extrapolate even further. For the nodes beyond 14A and N2, I have done nothing heroic but just assumed a regular 2 year cadence for both companies. The main point by this is that unless Intel and/or TSMC either stumble or somehow accelerate their cadence, the new status quo will simply remain the same, in favor of Intel.

Indeed, as is obvious in the graph, the combination of TSMC’s delay and Intel’s accelerated cadence is causing seismic changes with regards to the status quo of who will have process leadership going forward. In other words, Intel is now in pole position to reclaim and then retain process leadership for the rest of the decade.

- Intel could immediately take an up to 1.5x density leadership with 20A in the second half of 2024 (compared to N3).

- Given the pull-in of 18A, this lead could soon thereafter be extended to up to 1.8x. Intel will have a full node advantage for all of 2025.

- Although TSMC should reach parity with N2 in the first half of 2026, in reality this node will now compete against 14A due to Intel’s relentless pursuit of Moore’s Law. Although the exact gap will depend on the currently unknown scaling factors of these nodes, one can quite reliably extrapolate both companies’ historical scaling trends. In this scenario, Intel’s leadership would remain a very comfortable 1.6x.

- For Intel 10A in 2028, I have taken a more conservative 1.8x scaling (Intel’s shrinks are historically over 2x). But since TSMC hasn’t done a shrink over 2x for what should be a few decades now, as mentioned above the status quo will remain the same, with about a 1.6x lead for Intel.

In summary, it may be a bit overkill to extrapolate to 2028, this is actually completely irrelevant to determine who will have process leadership going forward, because the most important events are unfolding pretty much here and now (or in the near future): Intel’s accelerated cadence from 4 to 20A and TSMC’s delays at 3nm and 2nm.

Worse than Intel 10nm

Intel’s 10nm was arguably the biggest slip in the history of semiconductors. How could one do possibly worse than that? Well, TSMC seem to have some idea.

Simply put, mathematically speaking N3 + N2 taking 5.75 years for a combined shrink of ~2.9x (20% CAGR) is worse than Intel 10nm taking 5 years for a 2.7x shrink (22% CAGR).

Just let this sink in for a second. Hence, if 10nm was how Intel lost its process leadership, then N3 + N2 is how TSMC is losing its process leadership.

Risks and SemiWiki

Generally, I feel the analysis above is very robust. Intel showed an 18A (test) wafer at Investor Meeting and pulled in the schedule by up to half a year. These and other proof points are strong signals that this is a very healthy process that Intel is very comfortable and confident about.

Investors may wonder how this is possible. The answer is because Intel has separate development teams. One team is working on the 4/3 tick-tocks, while another team is busy with 20A and 18A. Further teams are researching the nodes and technologies beyond. Hence, the Intel 4 “defect mode” didn’t necessarily impact 20A. In short, Intel is back.

By contrast, I have extensively discussed the TSMC delays by now. Although TSMC maintains it is “on track”, in reality Moore’s Law allows one to call anything that is longer than two years a delay. Intel shows (at least with 20A) that a 2 year cadence (or even shorter) is still possible. Given TSMC’s latest disclosures, TSMC’s schedule until 2025 is now just as well confirmed as Intel’s.

However, admittedly, while the schedule/roadmap of both companies is now known, the exact specifications (like the scaling factors) are not. Therefore, for illustration I will review another analysis (published before TSMC’s Q1 earnings) on SemiWiki by an author that for the last few years has been quite bearish about Intel and bullish about TSMC (with regards to process leadership).

With that background, quite to my surprise the author proposed an expected density improvement for TSMC’s N2 of just 1.33x. For comparison, in the graph shown above I have taken a 1.8x improvement for TSMC, in line with TSMC’s historic trend. Although the author put N2 in 2025, this has now proven to be incorrect.

How about Intel? The author proposed a 1.8x improvement for Intel 4 and a 1.6x improvement for 20A. However, I could not disagree more. Note that the 1.8x is despite (as mentioned above) Intel having redesigned Intel 4 to use much more EUV layers. (For comparison, the reduction in EUV layers by TSMC at N3 resulted in a lower density, so if anything more EUV allows for a higher density. Although Intel did say several years ago that it would not be as aggressive anymore to prevent getting into trouble.)

Secondly, the 1.6x assumption is despite 20A being Intel’s second-gen EUV process and moving to RibbonFET and PowerVia. Note that RibbonFET is simply inherently more dense than FinFET, since essentially the fins/ribbons (which are laid out adjacent in FinFET) are instead stacked vertically.

Thirdly, former CEO Bob Swan literally said that 7nm and 5nm (now called 4 and 20A) would both be 2.0x shrinks.

Overall, although I wouldn’t completely rule out somewhat reduced scaling targets, I see no evidence for Intel going as low as 1.6x since Intel has done more than 2x for at least the half a dozen prior generations.

Financials and stock

The main thesis in this article is that TSMC will lose its technology leadership. In the old days this would only indirectly benefit Intel as Intel would have to compete against inferior products. But with Pat Gelsinger going all in on Intel Foundry Services (IFS), in the long-term a loss of process leadership means that TSMC can now directly lose customers to Intel.

Indeed, Intel has said that is has already lured (at least) 5 “whale customers”, including Qualcomm (QCOM) and Cisco (CSCO), so this is not just a hypothetical situation. IFS poses a real threat to TSMC, and given the tech trends discussed in this article, this frankly makes TSMC currently non-investible for the long-term.

However, there are a few caveats. Although for the sake of this article’s length not readily discussed, TSMC reported absolutely stellar financials. Combined with the lackluster stock performance over the last so many quarters, TSMC’s once very high valuation has deflated like a souffle under a sledgehammer over the last few years.

So for investors with a shorter-term time horizon, TSMC as a business doesn’t show any weaknesses, going out as far as the stock market usually tends to look. For example, TSMC is still busy with its massive fab buildout ($40-44B capex just in 2022 alone), and Intel has yet to ramp some of its big foundry projects such as Ponte Vecchio, Arc and Arrow Lake, all of which have tiled that are manufactured at TSMC.

Hence, in the near-term, TSMC is going exactly nowhere, and management literally said during the Q&A that it doesn’t have enough capacity in 2022 to fulfill all demand (despite the aforementioned monster capex, which suggests these trends will continue at least through 2023).

Inflation

While many are concerned about inflation, this actually provides another argument for TSMC still being a strong near-to-mid-term investment. Given (for now) TSMC’s important strategic position as partner (middle man) of many of the world’s largest tech companies, including Nvidia (NVDA), Qualcomm (QCOM), AMD (AMD) and even Intel, TSMC has been able to mitigate the impact of inflation by passing on its increased costs. In other words, TSMC has been increasing its wafer prices for customers.

Evidence for this trend is visible in TSMC’s increased gross margin, which was 55.6% in the most recent Q1 quarter compared to 52.4% in Q1 2021 and 51.8% in Q1 2020. TSMC indicated it had increased its gross margin target, so this higher gross margin will not be a transitory phenomenon. This shows a business (model) that is very inflation-resistant as TSMC has been able to increases its prices by more than its rising costs due to inflation.

Investor Takeaway

It really wasn’t that long ago that many people thought TSMC had become invincible. (But hey, I am an Intel bull and once thought that Intel was invincible too). The TSMC plus Apple (AAPL) combination was steamrolling the Intel dinosaur, the relic from the foregone PC days.

It is now turning out that nothing could have been further from the truth. The PC came roaring back to life with COVID-19, while Pat Gelsinger is rebuilding Intel as this iconic technology company.

The simultaneous combination of Intel’s acceleration and TSMC’s deceleration is causing an unprecedented change in process leadership that is occurring much faster, and also much more profound, than anyone would have expected. Certainly not after that day in July 2020 when Intel delayed 7nm, followed by the day that the stock dropped by 20%.

As detailed, TSMC currently seems to be going through similar difficulties as Intel as 10nm. In fact, management’s stance is also quite reminiscent to how Intel management for years continued to feed off their past glories, while remaining silent about and downplaying the issues about the present and future. In fact, TSMC is now taking these Intel practices to the next level by claiming that its nodes are “on track” (for comparison, Intel truthfully confirmed all four its 1 year delays; for some reason it was only the fourth 1 year delay, of 7nm, that investors started to notice).

Strictly speaking, though, TSMC may be speaking the truth: if you never announce any schedules, then you can tell investors any date you like without having to announce delays. Internally, management might previously have set much more aggressive schedules to its engineers, but investors will never know about this.

In any case, the simple fact of the matter is that in my previous coverage on TSMC’s N2 node, I had given it the benefit of the doubt. But because of the latest management comments, I had to reduce my expectations for N2 by a staggering 5 quarters.

In the end, you simply can’t delay a node by four or more quarters and expect to remain (as) competitive. This was true for Intel then, and it remains true for TSMC now. The knife cuts both ways, and now it is cutting into TMSC’s competitiveness big time.

Moore’s Law continues relentlessly. As I see no roadblocks for Intel going forward given how drastically the technology and management landscape has changed in just the last year (RibbonFET, high-NA EUV, Pat Gelsinger, etc.), one cannot do anything but to conclude that TSMC is finished.

It might hence only be a matter of time until these technology trends start to impact the financials and hence the stock (as it did to Intel eventually). The biggest and real threat is that customers jump ship to Intel Foundry Services, which has been announcing new fabs on an almost quarterly cadence for the last year. To be sure, TSMC certainly remains investible for at least the next three to five years, in part given the stock’s decreased valuation in the recent past (even despite TSMC’s beats and raises).

However, due to the technology evolution (which shows that Intel could attain a full node advantage by 2025 already), I believe the foundry market is now primed for disruption. As mentioned it turns out Intel is exquisitely well positioned to capitalize with IFS. Pat Gelsinger strikes back.

Be the first to comment